Forrest Brewer's Systems Synthesis Lab

The Systems Synthesis Lab specializes in the development of unconventional tactics to solve engineering problems, with coincident creation of analytic or systematic models. Without such analysis, techniques with high potential remain as isolated tricks on the frontier of engineering practice. For example, the scaling of physical dimensions (VLSI process and MEMS) in circuits and systems has consequences in that new, subtle, physical phenomena become important to system behavior. Collective Dynamics, is an analytic approach in which ensembles of weakly correlated system states are exploited to improve overall functional performance or reduce noise. Similarly, the performance of low-cost approximate computation schemes can be greatly enhanced via exploiting the formal convergence properties of feedback (sigma-delta) modulators in lieu of fully random processes.

Areas of Research include but are not limited to:

- CMOS VLSI design including radiation, cryogenic and ESD effects

- High performance Asynchronous Logic and System Design

- Low-latency sigma-delta bitstream computation for signal processing and control

- Formal Methods in the specification, analysis, and implementation of systems

Main Areas of Research

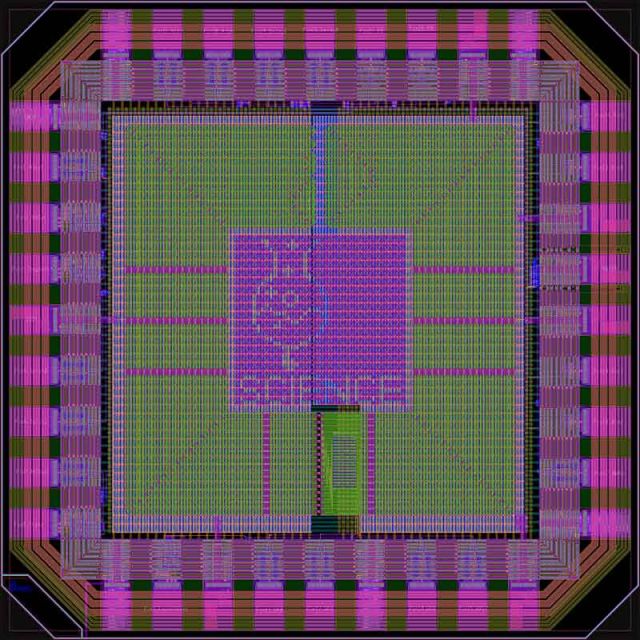

CMOS Pulse-Gate Asynchronous Logic

CMOS pulse gates are simple self-timed circuits that integrate an input signal and, if an internal threshold is passed, fire an output pulse while resetting the gate integrator. These gates provide practical means for constructing very high performance logic as standard cells, where PVT and clocking issues prohibit conventional CMOS solutions. At the opposite end of the spectrum, they promise single-digit fJ per event logic and neural processing in deep sub-threshold logic.

- Circuits and Applications

-

Pulse-Gate logic makes very low power, stable communication links possible in forbidding environments. In the high radiation environment of the Large Hadron Collider (LHC), logic faces the dual onslaught of extreme Xray fluence (equivalent to hundreds of MRad(Si) per year) and a veritable zoo of high energy particles with the potential for dozens of SEU hits in a clock cycle. Pulse gates substantially reduce the PVT variation from Xray dose while limiting the duration of SEU events to the generation of excess logic pulses. This allows for a relatively low cost hierarchical modular error mitigation scheme. Both asynchronous and synchronous mode communications are possible, as are alternative modulation modes (e.g. phase modulation).

- Clocking, Timing and Collective Phenomena

-

Measured pulse gate circuits exhibited anomalous stability and much lower timing jitter than expected. Observation and experimentation of this phenomena lead to the identification and analysis of pulse-collective phenomena where measured event timing jitter at an output is dependent on the total collection of coupled pulses in the circuit. Effectively, the circuit dynamics depend on the total momentum of the active pulses, and this stability is lent to all the outputs of the timing network. Analysis has led to unique circuits, ultra-stable pulse oscillators, and even closed-form analytic solution for simple circuit topologies.

- Verification

-

As pulse-gate circuits are asynchronous, they potentially inherit all the classical difficulties in such designs. Fortunately, the timing cycle of pulse-gates (integration, firing, reset) separates input and output event times with a dead-time, where the gate is insensitive to new pulses. In practical circuits, this can be approximated by a unit-time cycle model of state. In practice, clever designers promote certain outputs to become new effective timing gates, and since data and timing are present on any pulse event, these circuits can stably operate at very high performance. (Standard-cell layout of 10+GHz logic is possible for smaller logic circuits such as SERDES and parallel PRBS generation). Developing a formal verification strategy for such circuits guarantees correct logic behavior as well as improved layout.

- Pulse Gate based Spiking Neural Networks

-

The digital aspect of pulse gates is based on the input scale integrator. For small transistor sizes, these gate produce a simple analog CMOS neuron. Of particular import is the potential for very low power neural networks. The relative immutability of the output pulse signal and ease of creating both exhibitory and inhibitory behavior make these gates a natural analog for neurons. The potential for high performance at low power allows for application in LIDAR and RADAR signal analysis where substantial parts of the input information is buried in relative event timing phase.

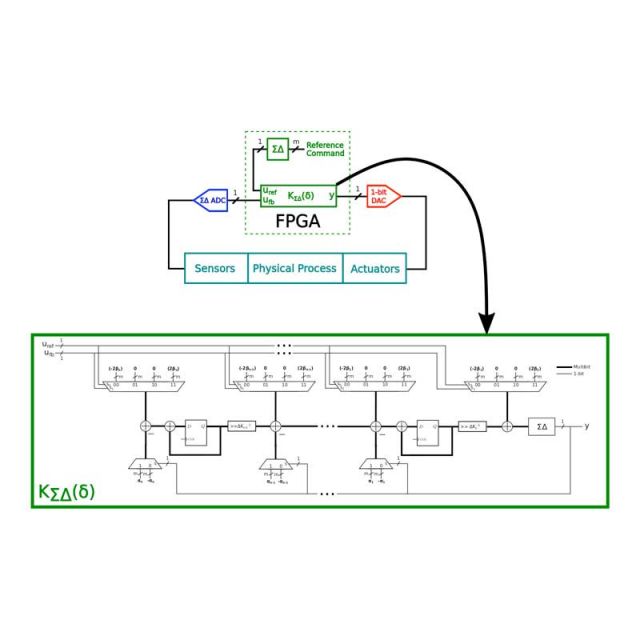

Sigma-Delta based Computation

Sigma-Delta modulation (PDM) is a binary non-place value data representation which is capable of very fast convergence when compared to statistical inference. For example, 256 binary samples of a variable between zero and 1 has an inferred accuracy little better than 1 part in 40. A binary (2nd order) sigma-delta signal has an inferred accuracy better than 1 part in 50,000. This and the inherent linearity of such modulators are reasons that they are the mainstay for high resolution medium frequency data conversion circuits. Conventionally, a sigma-delta bit-stream must be decimated several times to create accurate bit-parallel data for DSP. This process removes the redundancy, but adds considerable latency to the data. This project seeks to perform computation directly in the sigma-delta representation so that data need never be converted, allowing for substantially reduced footprint and power.

- Controls and Signal Processing

-

Here, the problem of constructing high-order filters for use in signal processing and in controls is explored. In particular, 16-bit resolution filters can be constructed without multipliers, given over-sampling ratios of 250. The resulting footprint is 10-15x smaller than conventional DSP, while practical 6th or 8th order stable filters can be realized in direct form using micro-power FPGAs such as Lattice ice40. Extensions to use 2 channel PDM and MASH techniques can extend the resolution to 24+ ENOB for these circuits. Applications include development of very low latency (near continuous time), high-resolution filters and controllers.

Brewer's Bio

Prof. Brewer has published over 100 papers and has 40 years experience in designing systems starting as a Senior Engineer at Northrop Corp. and as an academic for the last 30+ years. He holds a BS with honors in physics from Caltech and MS and Ph.D. degrees in Computer Science from the University of Illinois.

His early systems work involved defense programs in systolic-array based image processing architectures and digital feedback control. His Ph.D. work created the first processor-scale high-level synthesis system and his subsequent research co-created the PBS language (adopted by Synopsys Inc. and later by Accellera/System Verilog). His research in scheduling was used by Intel to create Itanium microcode and he served as an Intel faculty fellow in 1997. His research in symmetry applications lead to an LVS approach that was adopted by Mentor Graphics inc. in their flagship verification tool Calibre while his gate-level timing work with Prof. Sadowska was adopted by all the major EDA vendors. He has co-founded two startup companies and served on the technical boards of two others, including the recently acquired Atrenta Design Systems.

At UCSB, he co-founded the CE program and has served as its associate chair. He also created ECE 5 (with Prof. Hespanha), ECE 122a, ECE 122b, ECE 153a, ECE 224, ECE 253, ECE 256a, and ECE 256d (with Prof. Sadowska). He has been the IEEE student chapter faculty advisor for more than 20 years, overseeing its growth to the largest student organization on campus. He is a member of IEEE, APS, and ACM.

About the Lab

Interested in becoming a Systems Synthesis Lab member? Professor Brewer is looking for dedicated and hardworking students to join our team. If you are interested, please apply to the Electrical and Computer Engineering graduate program in the area of Computer Engineering. If you would like to send an email to Professor Brewer about your application, please include your CV and transcripts as well as a brief description of any past research experience.